1 Overview

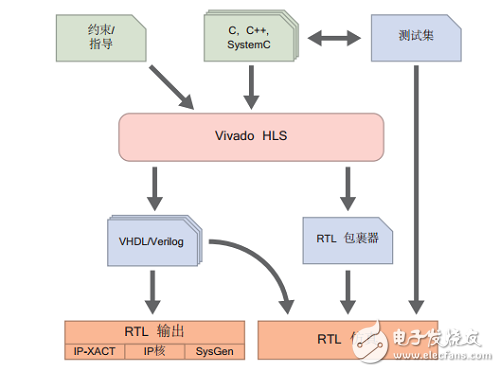

Vivado HLS is a tool provided by Xilinx and is part of the Vivado Design Suite. It can convert C-based designs (C, C ++ or SystemC) into RTL design files (VHDL / Verilog or SystemC for implementation on Xilinx fully programmable chips ).

1.1 The design process of vivado hls

Figure 1 vivado hls workflow

The Vivado HLS process is available in three different RTL formats. as follows:

IP-XACT — IP-XACT is a public specification document design IP proposed by the SPIRIT consortium. This is a widely used XML template for describing IP. It has nothing to do with specific tools and is machine-readable.

IP Core — When this option is selected, your IP will be exported to a format that can be imported into XPS.

SysGen — This option allows you to export the resulting RTL file into a package that can be used in the design of the System Generator.

1.2 Introduction to TCL scripts

TCL (early called "Tool Command Language", but it is not the same at present, but we still call it TCL) is a scripting language. Created by John Ousterhout. TCL is easy to learn and powerful. TCL is often used for rapid prototyping, script programming, GUI and testing. TCL is pronounced "Kick Knock" "TIckle".

2 labs2 use tcl script for c, c ++ to RTL level simulation synthesis

Use the project file fir.c fir.h fir_test.c of the labs1 in the previous section to run using the tcl script to complete the simulation, synthesis, and generation of ip and other actions of the entire project. Complete our design more conveniently and quickly.

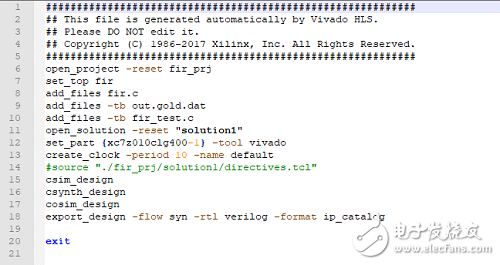

Run_hls.tcl script source code is as follows:

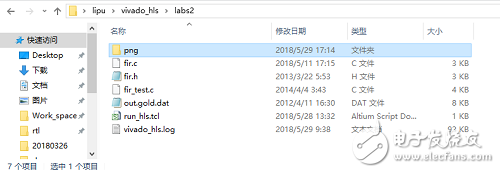

The Labs2 project directory is shown below. Includes files such as fir.c, fir.h, fir_test.c, out.gold.dat, and run_hls.tcl.

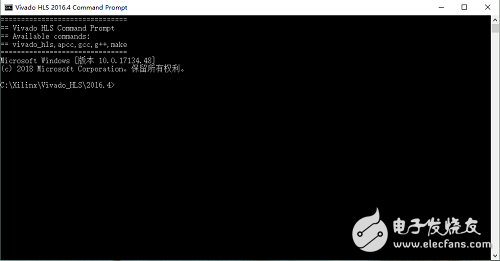

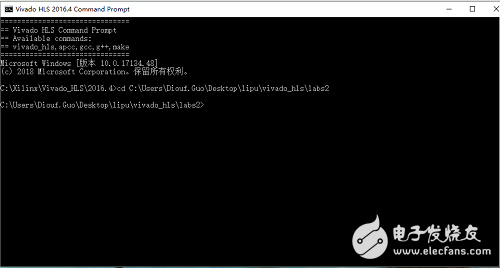

The first step is to open the vivado hls command prompt as shown below

The second step cd to the labs2 directory

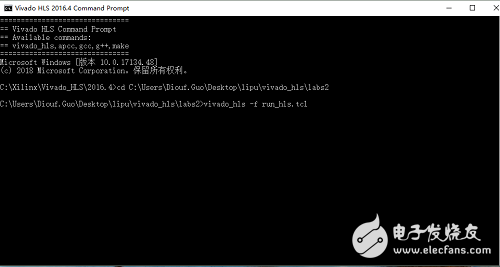

Step 3 Enter vivado_hls -f run_hls.tcl Enter

The process of running the entire script is as follows:

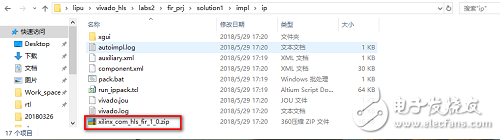

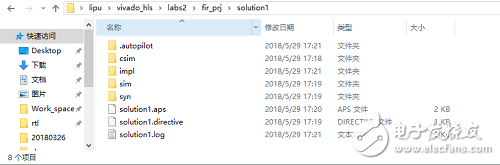

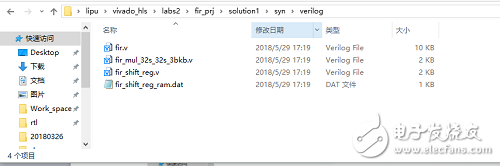

After running, the labs2 directory is as follows

Like labs1, we generated the verilog files of csim, sim, syn, impl and fir filters we needed. Completed the process of converting c into verilog. The next section will demonstrate how to add fir filter ip and vivado to generate modelsim simulation library and joint modelsim simulation fir filter.

Industrial Zinc Alloy Die Casting

Industrial Zinc Alloy Die Casting,Alloy Electroplating Die Casting,Custom Metal Die Cast Buckle,Zinc Alloy Pressure Die Casting Parts

Dongguan Metalwork Technology Co., LTD. , https://www.diecast-pro.com